從0開始學習Cadence Virtuoso 反相器Layout設計與后仿真

三、反相器Layout設計與后仿真

1. Layout設計基礎

在完成反相器的電路原理圖設計后,我們需要進行Layout(版圖)設計,這是集成電路物理實現的關鍵步驟。

Layout設計準備工作:

- 確保電路原理圖已經通過DRC檢查

- 確定工藝文件(PDK)已正確加載

- 熟悉工藝設計規則

- 了解器件尺寸和連接關系

2. 反相器Layout繪制步驟

a) 創建Layout視圖

在Library Manager中,為反相器cell創建Layout視圖,進入Virtuoso Layout Editor界面。

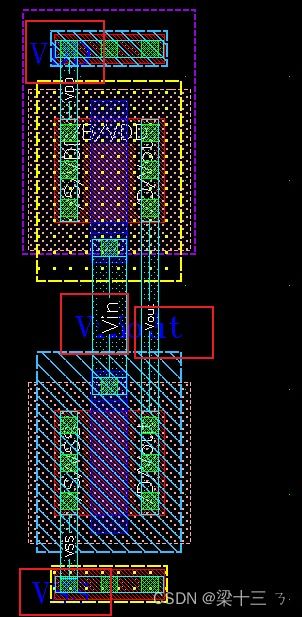

b) NMOS和PMOS器件放置

- 使用Create->Instance放置NMOS和PMOS晶體管

- 注意PMOS需要放置在N阱中

- 根據原理圖尺寸設置晶體管的W/L參數

- 確保器件間距滿足設計規則

c) 金屬連線

- 使用Metal1層連接源極和漏極

- 輸入信號連接到兩個柵極

- 輸出信號從漏極連接點引出

- 電源VDD使用Metal1連接到PMOS源極

- 地線VSS使用Metal1連接到NMOS源極

d) 接觸孔和通孔

- 在需要連接的不同層之間添加接觸孔(Contact)

- 多晶硅與金屬1之間需要添加相應的接觸孔

3. DRC檢查

完成Layout繪制后,必須進行DRC(設計規則檢查):

`

Verify->DRC

選擇相應的工藝規則文件

運行檢查并修正所有違規

重點關注:

- 最小間距

- 最小寬度

- 包圍規則

- 天線效應`

4. LVS驗證

LVS(版圖與原理圖對比)確保Layout與原理圖一致:

Verify->LVS

設置原理圖和版圖源

運行對比

檢查器件匹配、網絡匹配

修正不匹配項直到完全通過5. 寄生參數提取

在通過DRC和LVS后,進行寄生參數提取:

Verify->Extract

生成帶有寄生參數的網表

提取電阻、電容等寄生元件6. 后仿真設置

a) 創建后仿真配置

- 在ADE L界面創建新的仿真配置

- 選擇提取的寄生參數網表

- 設置與原理圖仿真相同的激勵和參數

b) 后仿真分析`

瞬態分析:觀察輸入輸出波形

直流分析:檢查電壓傳輸特性

交流分析:分析頻率響應

Monte Carlo分析:考慮工藝偏差`

7. 前后仿真對比

關鍵性能指標對比:

- 傳輸延遲時間

- 上升/下降時間

- 功耗

- 噪聲容限

- 驅動能力

常見差異分析:

- 寄生電容導致的延遲增加

- 寄生電阻引起的電壓降

- 耦合效應帶來的信號完整性問題

8. 優化與迭代

根據后仿真結果進行Layout優化:

- 調整器件尺寸

- 優化布線拓撲

- 減少寄生參數

- 改善匹配特性

9. 經驗總結

- Layout規劃很重要:在開始繪制前做好整體布局規劃

- 對稱性設計:保持電路對稱以獲得更好的匹配特性

- 電源完整性:確保電源和地線有足夠的寬度

- 信號完整性:關鍵信號線應盡量短且直

- 多次驗證:DRC、LVS必須完全通過才能進行后仿真

通過反相器的Layout設計和后仿真,我們建立了完整的集成電路設計流程,為更復雜電路的設計打下了堅實基礎。在實際項目中,這個過程需要反復迭代,直到所有性能指標都滿足設計要求。

如若轉載,請注明出處:http://www.ckbr.com.cn/product/10.html

更新時間:2026-01-07 06:11:06