數字集成電路測試系統的設計 原理、架構與實現

隨著現代電子技術的飛速發展,數字集成電路(IC)已成為各類電子設備的核心組成部分。為確保集成電路的可靠性、性能及功能完整性,設計高效、精確的測試系統顯得尤為重要。本文將系統闡述數字集成電路測試系統的設計原理、架構組成及實現方法,涵蓋測試需求分析、硬件平臺搭建、測試向量生成、結果分析與優化等關鍵環節。

一、測試系統設計概述

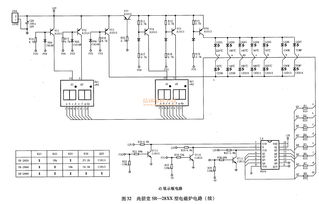

數字集成電路測試系統的主要目標是驗證芯片在制造過程中是否存在缺陷,并確保其符合設計規范。測試系統通常由測試設備、測試程序、接口適配器和數據分析軟件等部分組成。測試過程包括功能測試、參數測試和可靠性測試,需結合自動化技術以提高測試效率與覆蓋率。

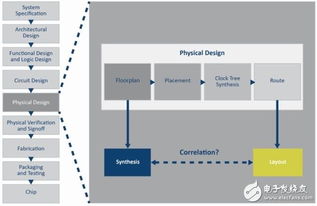

二、測試系統架構設計

- 硬件平臺:測試系統的硬件核心是自動測試設備(ATE),它負責生成測試信號、施加激勵并采集被測電路的響應。硬件平臺需包括高性能的數字通道、精確的時鐘源、電源管理模塊以及與被測芯片的接口適配器。可編程邏輯器件(如FPGA)常用于實現靈活的測試邏輯。

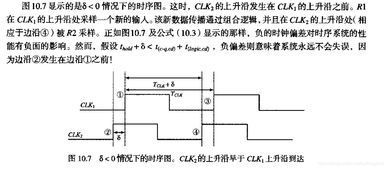

- 測試向量生成:測試向量是驗證集成電路功能的關鍵輸入序列。常用的生成方法包括確定性測試向量生成和隨機測試生成。通過故障模型(如固定故障、延遲故障)分析,設計高效的測試向量以覆蓋盡可能多的潛在缺陷。自動化工具如ATPG(自動測試模式生成)可大幅提升向量生成的效率。

- 軟件與控制:測試系統軟件負責控制硬件、執行測試程序并分析結果。軟件架構應包括測試序列編輯器、結果數據庫和用戶界面。通過集成腳本語言(如Python或TCL),用戶可自定義測試流程,實現自動化測試與數據分析。

三、測試流程與實現

測試流程通常分為預測試、核心測試和后測試三個階段。預測試包括設備校準與連接檢查;核心測試階段施加測試向量并采集響應;后測試則進行數據比較與故障診斷。為實現高精度測試,需考慮信號完整性、時序同步和噪聲抑制等問題。

四、挑戰與優化策略

數字集成電路測試面臨測試時間成本高、故障覆蓋率不足等挑戰。優化策略包括采用并行測試技術、引入邊界掃描(JTAG)標準以簡化測試訪問,以及利用機器學習算法進行智能故障預測。隨著集成電路工藝尺寸的縮小,測試系統需適應低電壓、高頻信號的測試需求。

五、未來發展趨勢

未來數字集成電路測試系統將向更高集成度、智能化和云平臺化方向發展。借助人工智能與大數據分析,測試系統可實現自適應測試與預測性維護,提升測試效率與準確性。同時,面向5G、物聯網等新興應用,測試系統需支持多協議、高速接口的驗證。

數字集成電路測試系統的設計是一個多學科交叉的工程領域,涉及電子工程、計算機科學和自動化技術。通過合理的架構設計與優化,測試系統能夠有效保障集成電路的質量與可靠性,推動電子產業的持續創新。

如若轉載,請注明出處:http://www.ckbr.com.cn/product/14.html

更新時間:2026-01-07 08:40:08