超大規模集成電路設計基本概念(二) 集成電路設計

在上一部分中,我們探討了超大規模集成電路(VLSI)的基本定義、發展歷程及其在現代電子技術中的重要性。本部分將深入解析集成電路設計的核心概念,包括設計流程、關鍵技術和面臨的挑戰。

一、集成電路設計的基本流程

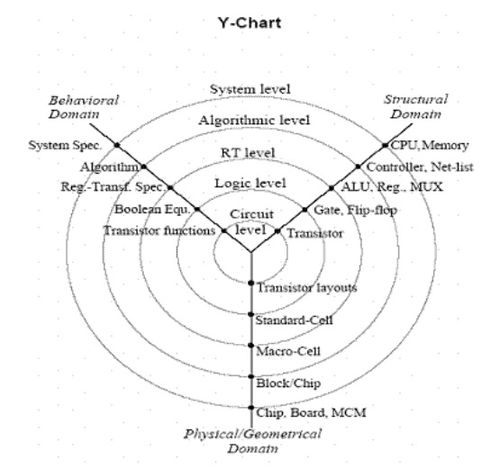

集成電路設計是一個系統化、多階段的過程,通常包括以下步驟:

- 需求分析:明確電路的功能、性能指標(如速度、功耗、面積)和應用場景。

- 架構設計:確定整體結構,如處理單元、存儲模塊和互連方式。

- 邏輯設計:使用硬件描述語言(如Verilog或VHDL)描述電路功能,并進行仿真驗證。

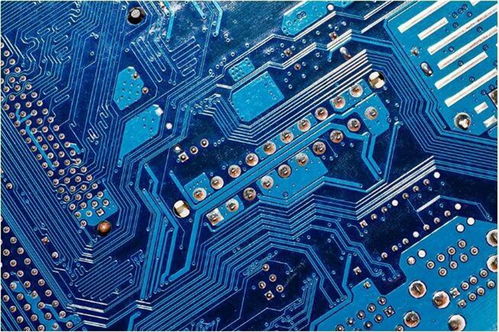

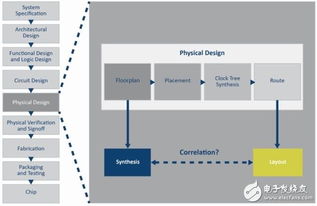

- 物理設計:將邏輯電路映射到物理布局,包括布局規劃和布線。

- 驗證與測試:通過仿真、形式驗證和實際測試確保電路正確性和可靠性。

二、關鍵技術解析

- 硬件描述語言(HDL):HDL是設計的基礎工具,允許工程師以文本形式描述電路行為。例如,Verilog和VHDL廣泛用于建模和仿真。

- 設計自動化工具:電子設計自動化(EDA)工具(如Cadence、Synopsys)幫助優化設計流程,包括邏輯綜合、布局和時序分析。

- 工藝節點:隨著工藝進步(如從28nm到7nm及以下),設計需考慮量子效應、寄生參數和熱管理問題。

三、面臨的挑戰

- 功耗管理:隨著集成度提高,功耗密度上升,需采用低功耗設計技術,如電源門控和動態電壓頻率調整。

- 信號完整性:高頻信號易受噪聲和串擾影響,要求精確的互連建模和屏蔽設計。

- 設計復雜度:超大規模電路包含數十億晶體管,需模塊化設計和復用策略以縮短開發周期。

集成電路設計是VLSI技術的核心,它融合了電子工程、計算機科學和材料學等多學科知識。隨著人工智能、物聯網等應用的發展,設計方法將持續演進,推動電子設備向更高性能、更低功耗的方向邁進。后續部分將探討設計驗證和未來趨勢。

如若轉載,請注明出處:http://www.ckbr.com.cn/product/23.html

更新時間:2026-01-07 22:23:34