航空/航天集成電路設(shè)計(jì) 探索高可靠、高性能的“太空芯”之路

在人類探索天空與宇宙的宏偉征途中,航空/航天集成電路(IC)扮演著如同“心臟”與“大腦”般至關(guān)重要的角色。從民航客機(jī)的飛行控制,到深空探測(cè)器的自主導(dǎo)航,高度集成、極度可靠的芯片是現(xiàn)代航空航天器的核心支撐。航空/航天集成電路設(shè)計(jì),是一個(gè)融合了尖端電子技術(shù)、極端環(huán)境工程與最高可靠性標(biāo)準(zhǔn)的獨(dú)特領(lǐng)域。

一、 嚴(yán)苛的設(shè)計(jì)要求:超越商業(yè)級(jí)標(biāo)準(zhǔn)

與消費(fèi)電子或工業(yè)級(jí)芯片不同,航空/航天IC設(shè)計(jì)首要面對(duì)的是極端且多變的物理環(huán)境。其核心要求可以概括為“三高”:

- 高可靠性:系統(tǒng)失效的代價(jià)是災(zāi)難性的,芯片必須在長(zhǎng)達(dá)數(shù)十年(如衛(wèi)星)的任務(wù)周期內(nèi),在無人維護(hù)的情況下穩(wěn)定工作。這要求設(shè)計(jì)采用容錯(cuò)、冗余、自檢等技術(shù),并經(jīng)過極其嚴(yán)格的測(cè)試與篩選。

- 高抗輻射性:在大氣層外,芯片會(huì)持續(xù)受到宇宙射線、太陽高能粒子等的轟擊,可能引發(fā)單粒子翻轉(zhuǎn)(SEU)、單粒子閂鎖(SEL)等效應(yīng),導(dǎo)致數(shù)據(jù)錯(cuò)誤甚至硬件永久損壞。設(shè)計(jì)上需采用特殊的抗輻射(Rad-Hard)工藝、加固電路(如DICE單元)和系統(tǒng)級(jí)防護(hù)策略。

- 寬溫區(qū)與高穩(wěn)定性:工作溫度范圍可能從深空的-270°C到再入大氣層或發(fā)動(dòng)機(jī)附近的數(shù)百攝氏度。芯片必須在整個(gè)溫度范圍內(nèi)保持性能穩(wěn)定,材料、封裝和熱設(shè)計(jì)都面臨巨大挑戰(zhàn)。

二、 核心技術(shù)路徑:從專用工藝到系統(tǒng)級(jí)創(chuàng)新

為滿足上述要求,航空/航天IC設(shè)計(jì)通常遵循幾條主要技術(shù)路徑:

- 工藝加固:采用特殊的半導(dǎo)體制造工藝,如絕緣體上硅(SOI)或藍(lán)寶石上硅(SOS),這些工藝能有效隔離輻射影響,降低漏電和閂鎖風(fēng)險(xiǎn)。

- 設(shè)計(jì)加固:在電路設(shè)計(jì)層面,廣泛應(yīng)用冗余設(shè)計(jì)(如三模冗余TMR)、糾錯(cuò)編碼(ECC)、硬化存儲(chǔ)器和鎖存器等。即使工藝本身不特殊,也能通過設(shè)計(jì)方法顯著提升抗干擾能力。

- 系統(tǒng)級(jí)容錯(cuò):在更高的系統(tǒng)架構(gòu)層面,通過多機(jī)備份、動(dòng)態(tài)重構(gòu)、故障檢測(cè)與隔離等技術(shù),確保即使部分芯片失效,整個(gè)系統(tǒng)功能仍能維持。

- 異構(gòu)集成與先進(jìn)封裝:隨著任務(wù)復(fù)雜度的提升,將處理器、存儲(chǔ)器、傳感器、射頻模塊等不同工藝、功能的芯片通過3D堆疊、硅中介層等先進(jìn)封裝技術(shù)集成在一起,成為實(shí)現(xiàn)高性能、小型化、低功耗的關(guān)鍵。這對(duì)于空間、重量、功耗都極其受限的航天器尤為重要。

三、 應(yīng)用場(chǎng)景與挑戰(zhàn)

- 航空電子(Avionics):包括飛行控制計(jì)算機(jī)、導(dǎo)航系統(tǒng)(如GPS/INS)、通信與數(shù)據(jù)鏈、發(fā)動(dòng)機(jī)控制單元(FADEC)等。這些芯片要求高可靠性、高實(shí)時(shí)性和功能安全認(rèn)證(如DO-254標(biāo)準(zhǔn))。

- 航天任務(wù):

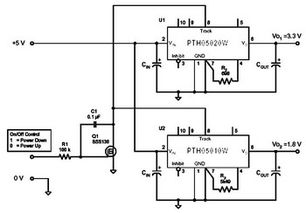

- 衛(wèi)星平臺(tái):姿態(tài)與軌道控制、電源管理、星載數(shù)據(jù)處理等芯片,是衛(wèi)星長(zhǎng)期在軌工作的基礎(chǔ)。

- 深空探測(cè):探測(cè)器上的科學(xué)載荷數(shù)據(jù)處理、自主導(dǎo)航與避障(如火星車)、深空通信等,對(duì)芯片的算力、能效和自主性提出了更高要求,同時(shí)必須耐受長(zhǎng)期的深空輻射環(huán)境。

- 載人航天:涉及生命保障、環(huán)境控制、人機(jī)交互等系統(tǒng),對(duì)安全性和可靠性的要求達(dá)到頂峰。

當(dāng)前面臨的主要挑戰(zhàn)包括:

- 性能與可靠性的平衡:最先進(jìn)的商用制程(如5nm、3nm)性能卓越,但通常對(duì)輻射極為敏感,且長(zhǎng)期可靠性數(shù)據(jù)不足。如何在利用先進(jìn)算力的同時(shí)確保航天級(jí)可靠性,是巨大難題。

- 成本與周期:特種工藝研發(fā)、流片、長(zhǎng)達(dá)數(shù)年的嚴(yán)格測(cè)試與認(rèn)證,導(dǎo)致航天級(jí)芯片成本極其高昂,研發(fā)周期漫長(zhǎng)。

- 自主可控與供應(yīng)鏈安全:在全球地緣政治背景下,建立自主、安全、可靠的航空/航天集成電路設(shè)計(jì)、制造與供應(yīng)體系,已成為國家戰(zhàn)略能力的核心組成部分。

四、 未來展望

航空/航天IC設(shè)計(jì)將朝著以下方向發(fā)展:

- “芯粒”(Chiplet)與異構(gòu)集成:通過將不同工藝、功能的“芯粒”集成,既能利用先進(jìn)商用工藝的高性能,又能將關(guān)鍵核心功能用加固單元實(shí)現(xiàn),是平衡性能、可靠性與成本的有效途徑。

- 智能與自主化:隨著人工智能在軌處理、星上智能決策等需求增長(zhǎng),設(shè)計(jì)面向航天應(yīng)用的專用AI加速芯片(Space AI Chip)成為熱點(diǎn)。

- 設(shè)計(jì)與驗(yàn)證方法學(xué)革新:利用更先進(jìn)的EDA工具,進(jìn)行輻射效應(yīng)仿真、可靠性預(yù)測(cè)和系統(tǒng)級(jí)協(xié)同設(shè)計(jì),以縮短研發(fā)周期,降低成本。

- 商業(yè)化與標(biāo)準(zhǔn)化:在低軌衛(wèi)星星座、太空旅游等商業(yè)航天浪潮推動(dòng)下,催生了對(duì)“性價(jià)比”更高的“商業(yè)航天級(jí)”(Commercial Off-The-Shelf, COTS with qualifications)芯片的需求,可能推動(dòng)相關(guān)標(biāo)準(zhǔn)和技術(shù)生態(tài)的演進(jìn)。

航空/航天集成電路設(shè)計(jì)是一門在極限約束下追求極致可靠與性能的藝術(shù)與科學(xué)。它不僅直接關(guān)系到飛行器的安全與任務(wù)成敗,更是衡量一個(gè)國家航空航天與高端芯片產(chǎn)業(yè)核心競(jìng)爭(zhēng)力的關(guān)鍵標(biāo)尺。隨著人類邁向更深遠(yuǎn)的太空,這顆“太空芯”必將跳動(dòng)得更加穩(wěn)健而有力。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.ckbr.com.cn/product/56.html

更新時(shí)間:2026-01-05 16:15:35